TR-393

Preliminary Evaluation of the connection network for the Multi-PS1 System

by

K. Masuda, H. Ishizuka, H. Iwayama(Mitsubishi),

K. Taki and E. Sugino

June, 1988

©1988, ICOT

Mita Kokusai Bldg. 21F 4-28 Mita 1-Chome Minato-ku Tokyo 108 Japan

(03) 456-3191~5 Telex ICOT J32964

# Preliminary Evaluation of the connection network for the Multi-PSI system

Kanae MASUDA, Hirokazu ISHIZUKA, Hiroaki IWAYAMA Mitsubishi Electric Corporation, 325 Kamimachiya, Kamakura-shi, Kanagawa 247 JAPAN,

Kazuo TAKI, Eiji SUGINO Institute for New Generation Computer Technology(ICOT), 4-28, Mita 1-chome, Minato-ku, Tokyo 108 JAPAN,

### Abstract

The Multi-PSI system has been developed in the Fifth Generation Computer Systems(FGCS) project in Japan. It is an experimental parallel machine mainly used for the parallel software research.

Network-connected multiprocessor systems like the Multi-PSI have such a nature that interprocessor communication costs much higher than intra-processor processing, which affects the system performance. However, measurements of the communication cost for a realistic multiprocessor system have rarely been seen.

This paper describes the network system of the Multi-PSI-V1 system and measurement of the interprocessor communication cost for the network system.

### 1 Introduction

The Parallel Inference Machine (PIM) is one of the most important research themes of Japan's FGCS project. In the first three-year stage of the project, PIM research sought to develop basic technologies of machine architecture and parallel execution mechanisms, and accumulated several methods for constructing machine hardware and parallel execution methods of logic programs [2]. But several serious problems of parallel software were revealed by the research, and we recognized that parallel software research has to be done along with parallel architecture research.

We think it is important to prepare a research and development environment for parallel programs first in which programs can be executed in parallel and developed and evaluated efficiently. So we plan two systems; the first is Multi-PSI-V1(version1) focusing on ease of realization, and the second is Multi-PSI-V2 improving machine scale, functions, and speed.

Figure 1: Multi-PSI-V1 system

#### (1)Multi-PSI-V1

Multi-PSI-V1 contains 6 to 8 PSI machines connected by a dedicated lattice network; each PSI has its own I/O devices (see figure 1) [6]. The purpose is to implement a prototype of KL1(Kernel Language version 1) language processing system experimentally in a short period [7]. The parallel logic programming language KL1 is based on GHC and implemented in ESP, the sequential system description language of PSI [1] [8].

#### (2)Multi-PSI-V2

A smaller and faster version of the PSI machine(PSI-II) without I/O is used for the PEs, and 16 to 64 PEs are connected with a new version of the network, which is improved in speed and functions [5]. One PSI machine is used as a front-end processor. The KL1 language execution system is written in firmware to realize high execution speed. The PIMOS(Parallel Inference Machine Operating System) is implemented, and the dynamic load balancing method, parallel algorithms, and

large-scale parallel application programs are studied.

Network-connected multiprocessor systems like the Multi-PSI have such a nature that inter-PE communication costs much higher than intra-PE processing. This fact strongly affects the system performance when the inter-PE communication rate increases. It is important to know the inter-PE communication cost for the researches of load balancing and parallel algorithms. However, measurements of the communication cost for a realistic multiprocessor system have rarely been seen.

This paper describes the network system of the Multi-PSI-V1 system and measurement of the inter-PE communication cost for the network system coupled with KL1 language processing system, a realistic parallel language processor.

## 2 Connection Network of Multi-PSI-V1 System

#### 2.1 Overview of the System

The PEs are PSI machines, 6 to 8 PEs being connected on a dedicated lattice network. There is no shared memory. Inter-PE communications are performed by exchanging message packets. A user does not handle special message primitives, but simply writes goals with pragmas and unifications. The pragma is an annotation which allows the programmer to specify explicitly how the goals should be assigned to the processors. Inter-PE communication messages are automatically generated by the language execution system. There are two major message types; one concerns KL1 goal management, such as goal sending and termination reporting; and the other concerns unification across the PEs. Each PE has a different address space, and when a reference pointer is passed from one PE to another PE, the internal address of the source PE is converted to a global identifier(ID) and then sent [3]. The address translation table between internal address and global ID is maintained in each PE.

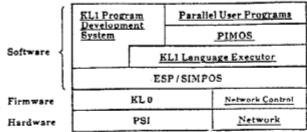

Figure 2 shows the configuration of Multi-PSI-V1. The underlined sections have been newly developed, and the other sections represent the PSI machine system itself.

#### 2.2 Connection Network Hardware

We think that the network-connected structure is essential for large scale multiprocessor systems. We also think that a network, in which logical inter-PE distance is not uniform like mesh, hyper cube, etc., is important for very large scale systems. From

Figure 2: Configuration of the Multi-PSI-V1

this reason, we chose mesh network for the Multi-PSI to study load balancing method and parallel algorithms which can be applied to very large scale multiprocessor systems.

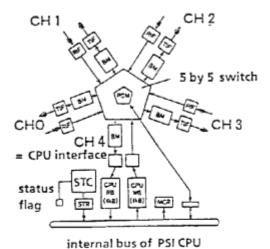

Figure 3 shows the block diagram of the network hardware. It is installed in the option slots of CPU internal bus, and four cables are used to connect adjacent four PEs. Each connection of PE to PE is called a channel. A channel contains two signal sets, one is for transmission and another is for receiving. Data is transferred in 10-bit parallel containing a parity bit. The transmission rate is approximately 500k bytes/sec for each direction.

Message packets are constructed by software. Each packet has a destination PE number in the packet header. The network recognizes the destination PE number, and if equal to its own, the network takes the packet into its receiving buffer. If the PE number is different, the network looks up the path table to get the channel number to which the packet should be re-transmitted. There are simple routing methods which avoid this network deadlock. One involves passing the packet to the horizontal direction prior to the vertical direction when the packet should be passed to the PE on the diagonal direction.

## 3 Evaluation of the Connection Network System

#### 3.1 Objectives

The inter-PE communication cost contains network transfer cost and cost of pre- and post-processing for the network transfer. The former is affected by the inter-PE distance, the latter is not. These pre- and post-processing contain inter-PE goal management, address translation, and data format conversion for the network transfer. These processing cannot be

PDM :path table

TIF :transmitting interface

RIF :receiving interface

BM :buffer memory

CPUWB:CPU write buffer

CPURB :CPU read buffer

MCR :mode control register

STR :status register

Figure 3: Block diagram of the Network Hardware

removed from the execution system of an networkconnected multiprocessor system. It is very important to know the inter-PE communication cost and its components not only for parallel software research like load balancing and parallel algorithms but also for network design and tuning of parallel language processing system.

The objective of the evaluation is to show the inter-PE communication cost and its components for the Multi-PSI-V1 system, a realistic parallel processing system of the logic programming language KL1. The other objective is to make an estimation of those costs for the Multi-PSI-V2, more powerful and practical system than Multi-PSI-V1. We expect that the measuments will give an order of the cost value which can be used practically in the study of load balancing, parallel algorithms, etc.

Multi-PSI-V1 consists of the KL1 language processing system and the connection network system. The hierarchical structure of the connection network system is as shown in figure 4.

#### (1) The KL1 Processing System

This is a language processing system written in ESP that executes and controls KL1 programs.

#### (2)Network Handler

This takes the messages from the language processing system, formats them into byte sequences, and passes them to the handler ker-

| KL1<br>Processing<br>System |               |       | Network<br>Hardware |       |               |       |  |

|-----------------------------|---------------|-------|---------------------|-------|---------------|-------|--|

| (ESP)                       | (ESP)<br>P£ri | (F/V) | (8/%)               | (F/N) | (ESP)<br>PE#1 | (ESP) |  |

Figure 4: Layered structure of the Network System

nel, also performing the corresponding reverse conversion processes. It also handles the KL1related goal management for transmission and reception, and address translation. It is written in ESP.

#### (3) Handler Kernel (Network Support Firmware)

This takes the byte sequences from the network handler, and performs conversion in both directions between byte sequences and network packets. The handler kernel is implemented as firmware in KLO evaluable predicates.

#### 3.2 Measurement Methods

#### 3.2.1 Basic concept about the Measurements

We measured the various data and assessed them in terms of the following two main items to evaluate the connection network system [4]:

- Comparison of intra-PE and inter-PE processing performances (in terms of the processing time for a single reduction). We found the time taken to perform one reduction on a single PE, and the time to perform it on two PEs, and discussed the macro performance of the connection network system.

- (2) Analysis of dynamic characteristics of each layer of the connection network. More detailed analysis of the data from (1) above, yields a quantitative estimate of the comparative cost (in time) of using the different layers of the connection network system.

Here, we chose to take the time to perform one reduction on a two-PE multi-PSI. In other words, we defined the comparative intra-PE and inter-PE performance as the ratio of the time taken to perform the reduction for a given goal on a single PE to the time taken to perform the reduction for the same goal on the other PE after sending it to the other PE and receiving the reply back. This is an

```

test3_la(0) :- true | true.

test3_1a(N) :- Ni := N-1 | wait3_1a(R,Ni),

call(bench_mark@t3_la.R._).

wait3_la(success,N) :- true | test3_la(N).

t3_la :- true | alloc(5)@@tt3a(x).

tt3a(X) :- true | X=atom.

```

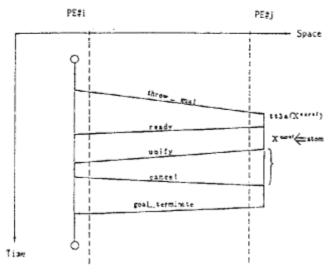

Figure 5: An example of the bench-mark program(unify test)

Figure 6: An example of the message exchange

extremely important parameter when writing KL1 programs, in deciding how much the rate of inter-PE communication is allowed against the intra-PE processing. A number of benchmark programs of the type shown in figure 5 were prepared, and execution time measured (see figure 6). We took the total of thirteen orders for inter-PE communications ("throw\_goal", "unify", "read", etc.) and measured the cost for varying types of arguments and numbers of executions of them. We timed them by looping each program 100 times, taking the average time to reduce the variance of the timer supported by the operating system.

#### 3.2.2Communication cost for Different Layers

(1) Handler communication cost (Ha) can be de-

in accordance with the principles given in 3.2.1, and deducting from this the cost of the handler kernel (F) and of the network hardware (H):

$$Ha = L - F - H$$

where F and H are as described in items (2) and (3) below.

- (2) Handler kernel cost (F) is measured by the GEVC counter, which counts the execution time for evaluable predicates such as "mpsi\_ write\_buffer" and "mpsi\_read\_buffer",etc., that either read data from or write it to the interface registers one byte at a time.

- Network hardware communication cost (H) is derived from analysis of hardware operation.

#### Measurement Results and Con-3.3sideration

Consider the first item, the comparison between the intra-PE and inter-PE performances. First selecting particularly important items like "throw\_goal", "unify" and "read" from among theinter-PE communication orders, we investigated the communication costs.

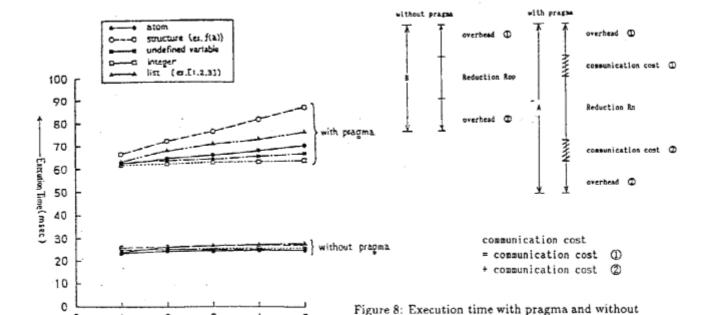

Figure 7 shows the results of running different benchmark programs with different argument types (atom,integer,undefined variable,structure,list) and different argument numbers(1,2,3,4,5).

The vertical axis of the graph is the average time taken for the one execution of 100 loops, and shows both the time taken when the goal is assigned to a different PE (with pragma) and when the goal is handled within the PE (without pragma). The difference between the time (A) with pragma and (B) without pragma can be taken as an approximation to the communication cost. It is important to note that reductions are of two types: those that have been optimized, and those that have not. In our benchmark programs, those without pragmas have been optimized, but those with pragmas have not (see figure 8 for Rop and Rn). When calculating the communication cost, it is not enough to know the difference in execution time; account must also be taken of the difference in the reduction time. In fact, therefore, the communication cost (L) is given by the following equation:

L = execution time A (with pragma) - execution time B (without pragma) - (reduction time Rn - reduction time Rop)

Note that the optimized reduction time Rop rived by taking the time of execution (L) found (1.12msec) and the non-optimized time Rn

pragma

Figure 7: Execution time for predicate argument numbers(throw\_goal)

3

→ Number of Arguments

4

5

2

0

۲

(2.25msec) were measured using a different benchmark program.

Again, the ratio of the inter-PE communication processing time to the intra-PE processing time is given by the following equation:

Processing time ratio = ( L + Rm ) / (Rm)

Table 1 gives the ratios, R, derived from the processing times (A,B) with and without pragma for different types and numbers of arguments.

It is clear from this table that, although there is some scatter in the processing time ratio, R, it is generally about 20:1. This indicates that it takes about 20 times longer to perform the reduction for the same goal by addressing another PE and waiting for the reply than by performing it within the same PE. It means that the inter-PE communication consumes much more processing time than a goal reduction within a PE, and the communication degrades the system performance. The volume of inter-PE communition processing should be reduced by these corresponding amount.

Now let us consider the second item, of determining the communication cost for each level of the network. In this respect, the size of the packet for orders ("throw\_goal", "read", "unify", etc.) is fixed for each type of argument, enabling calculation of communication cost for firmware (the handler kernel)

and hardware, and this in turn enables the handler communication cost to be calculated (see table 1).

Table 1 shows that the ratios of the hardware cost and firmware cost are much lower than the handler communication cost, approximately in the ratio of 1:3:500. It means that the communication bottleneck is not the hardware message transmission but the software message processing in this system.

Finally, let us extrapolate these results to Multi-PSI-V2. The speed of the handler is expected to increase by about 100-fold, and the network hardware by about 5-fold. The processing time ratio for the Multi-PSI-V1,

will change into the following for the Multi-PSI-V2:

```

Ratio = (handler cost/100

+ firmware cost + hardware cost/5

+ one reduction cost/100)

/ (one reduction cost/100)

```

Take the case at the head of table 1. This calculation yields a value that increases from 17.8 to 28-fold.

This implies that the inter-PE communication cost for the V2 system will be higher than the V1 system, or rather that the volume of inter-PE processing in the V2 system should be reduced by the corresponding amount.

Table 1: Results of execution time with pragma and without pragma

|                                                         |          |                                                                        |                                                             |                                                             |                                                             |                                                      |                                              |                                                             | (msec)                                               |

|---------------------------------------------------------|----------|------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------|------------------------------------------------------|

| Measurement<br>Items                                    | ,        | Irguments                                                              | Results                                                     |                                                             | Communi-<br>cation<br>Cost                                  | F/Ni                                                 | H/W                                          | Handier                                                     | Proce-                                               |

| (Commication                                            | <u> </u> |                                                                        | 1                                                           |                                                             | (Ea+F+H)                                                    | Cost                                                 | Cost                                         | cost                                                        | Time<br>Ratio                                        |

| Orders)                                                 | No       | Types                                                                  | ٨                                                           | В                                                           | L                                                           | F                                                    | H                                            | Ha                                                          | R                                                    |

| throw_goal<br>(including<br>ready, goal<br>_terminates) | 1        | aton<br>undef<br>integer<br>structure<br>list(1)<br>list(2)<br>list(5) | 62.72<br>62.61<br>61.96<br>66.62<br>63.10<br>64.33<br>66.80 | 23.90<br>24.36<br>24.76<br>25.41<br>23.40<br>24.11<br>25.39 | 37.69<br>37.12<br>36.07<br>40.08<br>38.57<br>39.09<br>40.28 | 0.23<br>0.23<br>0.22<br>0.24<br>0.24<br>0.24<br>0.25 | 0.07<br>0.07<br>0.07<br>0.07<br>0.07<br>0.07 | 37.39<br>36.82<br>35.78<br>39.77<br>38.26<br>38.78<br>39.94 | 17.8<br>17.5<br>17.0<br>18.8<br>18.1<br>18.4<br>18.9 |

|                                                         | 2        | atce<br>undef<br>integer<br>structure<br>list( )                       | 64.90<br>63.61<br>62.51<br>72.42<br>68.49                   | 24.17<br>24.60<br>25.11<br>26.06<br>26.44                   | 39.60<br>37.88<br>36.27<br>45.23<br>40.92                   | 0.24<br>0.25<br>0.23<br>0.26<br>0.26                 | 0.08<br>0.08<br>0.07<br>0.08<br>0.08         | 39.28<br>37.55<br>35.97<br>44.89<br>40.58                   | 18.6<br>17.8<br>17.1<br>21.1<br>19.2                 |

|                                                         | 3        | atom<br>undef<br>integer<br>structure<br>list( )                       | 66.62<br>64.78<br>63.27<br>76.92<br>71.53                   | 24.11<br>24.57<br>25.09<br>26.24<br>26.66                   | 41.36<br>39.08<br>37.05<br>49.55<br>43.74                   | 0.26<br>0.27<br>0.23<br>0.23<br>0.28                 | 0.08<br>0.08<br>0.07<br>0.09<br>0.09         | 41.04<br>38.73<br>36.75<br>49.18<br>43.37                   | 19.4<br>18.4<br>17.5<br>23.0<br>20.4                 |

|                                                         | 4        | atce<br>undef<br>integer<br>structure<br>list(1)                       | 68.64<br>66.12<br>63.42<br>82.01<br>73.83                   | 24.19<br>24.68<br>25.16<br>26.54<br>27.01                   | 63.32<br>40.31<br>37.13<br>54.34<br>45.69                   | 0.27<br>0.28<br>0.24<br>0.30<br>0.30                 | 0.09<br>0.09<br>0.07<br>0.10<br>0.10         | 42.96<br>39.94<br>36.82<br>53.94<br>45.29                   | 20.3<br>18.9<br>17.5<br>25.2<br>21.3                 |

|                                                         | 5        | aton<br>undef<br>integer<br>structure<br>iist( )                       | 70.62<br>67.11<br>64.05<br>87.13<br>76.70                   | 24.13<br>24.69<br>25.13<br>26.73<br>27.18                   | 45.36<br>41.29<br>37.79<br>59.27<br>48.39                   | 0.29<br>0.30<br>0.24<br>0.33<br>0.33                 | 0.09<br>0.09<br>0.08<br>0.10<br>0.10         | 44.98<br>40.90<br>37.47<br>58.84<br>47.96                   | 21.2<br>19.4<br>17.8<br>27.3<br>22.5                 |

| unify<br>(including<br>cancel)                          | 1        | atom<br>undef<br>integer<br>structure<br>list(I)                       | 87.99<br>88.46<br>88.99<br>89.46<br>87.13                   | 28.34<br>28.78<br>29.21<br>29.66<br>27.53                   | 22.89<br>22.94<br>23.02<br>23.22<br>22.89                   | 0.14<br>0.14<br>0.13<br>0.15<br>0.15                 | 0.04<br>0.03<br>0.04                         | 22.71<br>22.76<br>22.86<br>23.63<br>22.70                   | -                                                    |

| read<br>(including<br>read_answer)                      | ı        | atou<br>undef<br>integer<br>structure<br>list(1)                       | 101.44<br>100.31<br>106.13<br>101.11                        | 70.45<br>71.10<br>72.03<br>69.15                            | 30.99<br>29.21<br>34.10<br>31.96                            | 0.12<br>0.11<br>0.13<br>0.13                         | 0.04<br>0.03<br>0.04<br>0.04                 | 30.53<br>29.07<br>33.93<br>31.79                            | -                                                    |

A : with pragme

It was shown that the inter-PE processing costs around twenty times more expensive than the intra-PE processing and the communication bottleneck is not the hardware message transmission but the software message processing in this system. Networkconnected multiproccessor systems like the Multi-PSI may have these characteristics in general. In such case, these measurements can be applied to give a guideline of the maximum inter-PE communicaion rate which does not reduce the system performance much.

It was also shown that the communication frequency on the Multi-PSI-V2(high performance and more practical model) would have to be maintained lower than the V1 system.

The Multi-PSI-V2 system is under development, on which the dynamic load balancing method, parallel algorithms, and large-scale parallel application programs will be studied.

### Acknowledgments

The authors would like to thank Dr.Shunichi Uchida and other members of Fourth Laboratory of ICOT for their valuable suggestions.

#### References

- [1] T. Chikayama. Unique features of ESP. In Proceedings of FGCS '84, 1984.

- [2] S. Goto and S. Uchida. Toward a High Performance Parallel Inference Machine - The Intermediate Stage Plan of PIM-. ICOTTR TR-201. ICOT, 1986.

- [3] N. Ichiyoshi, et al. A Distributed Implementation of Flat GHC on the Multi-PSI. In Proceedings of the 4th International Conference on Logic Programming, 1987.

- [4] K. Masuda, et al. Network Evaluation of the Multi-PSI system. In Proceedings of the 34th Conference of IPSJ(in Japanese), 1987.

- [5] H. Nakashima, et al. Hardware Architecture of the Sequential Inference Machine: PSI-II. In Proceedings of 4th Symposium on Logic Programming, 1987.

- [6] K. Taki, et al. Hardware design and implementation of the personal sequential inference machine(PSI). In Proceedings of FGCS '84, 1984.

- [7] K. Taki. The parallel software research and development tool : Multi-PSI system. In Proceedings of France-Japan Artificial Intelligence and Computer Science Symposium 86, October

- [8] K. Ueda. Guarded Horn Clauses. ICOTTR TR-103, ICOT, 1985.

B : without pra : A-8+1.12-2.25

<sup>:</sup> Mard-are Cost : Ka = L-F-H R : (L+2.25)/2.25

Conclusion